## Welcome to DESIGNCON® 2022 WHERE THE CHIP MEETS THE BOARD

#### Conference

April 5 – 7, 2022

**Expo** April 6 – 7, 2022

Santa Clara Convention Center

#DesignCon

# Validation Shift-Left: Enabling Early SerDes Mixed-Signal Validation

David Halupka (SeriaLink Systems)

David Halupka, Aleksey Tyshchenko (SeriaLink Systems) Richard Allred, Marc Erickson, Tripp Worrell, Barry Katz, Jesson John (The MathWorks) Venu Balasubramonian, Lenin Patra (Marvell Semiconductor), Ranjan Sahoo (NXP)

#DesignCon

#### **SPEAKER**

#### David Halupka, PhD

*Co-Founder, SeriaLink Systems* david@serialinksystems.com | www.serialinksystems.com

David has over 20 years of experience in mixed-signal and embedded system design. He was with Kapik for 11 years, where he served as Senior System-Architect and Principal Engineer and led the digital design team. In 2018, he joined Intel's Mixed Signal-IP Group as Senior Systems Engineer, where he was responsible for adaptation algorithm development for the multi-standard SerDes. Ph.D, M.A.Sc., and B.A.Sc. from the University of Toronto.

SeriaLink Systems is a consulting team focusing on system modeling of high-speed serial links, IBIS AMI modeling, model correlation and system validation. SeriaLink Systems is working on building a configurable modeling flow to support SerDes projects through their entire life cycles: from architecture definition, through analog and digital design, to design validation

#DesignCor

informa markets

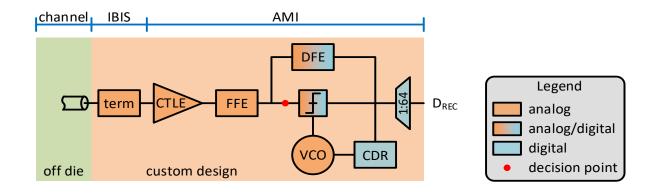

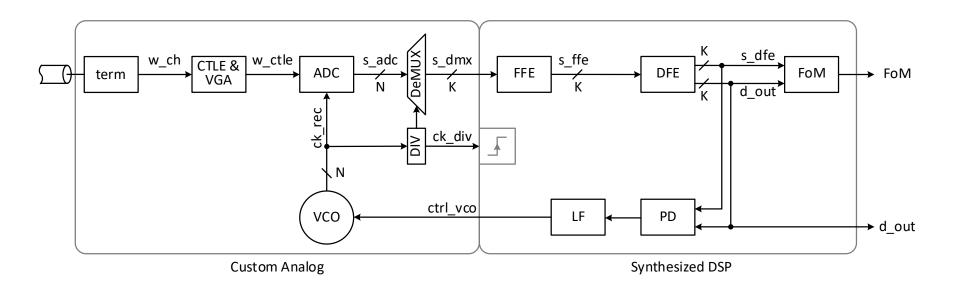

### **Motivation: Legacy SerDes**

- Legacy-based SerDes used analog circuits for RX equalization

- Digital subsystem used for post-equalization deserialization, adaptation control, analog calibration

#DesignCon

Digital/analog interaction mainly one-way: consumer/producer type of interaction

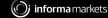

### **Motivation: SerDes Complexity is Increasing**

- Modern SerDes are increasingly mixed-signal: equalization is split between analog and digital domains

- Closed-loop analog/digital interaction is increasing, e.g., CDR loop crosses digital/analog boundary 2×

#DesignCon

- Digital systems (not shown) control calibration tuning of analog sub-systems as well

- Digital/Analog validation becomes increasingly more important

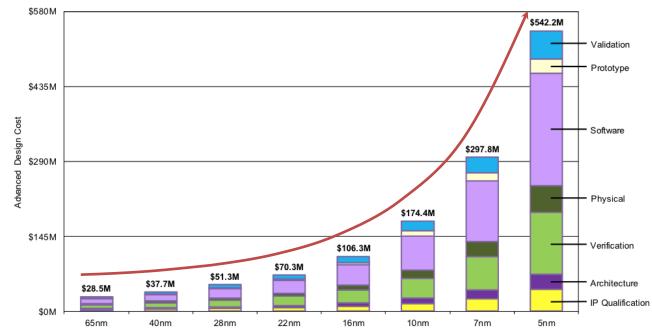

### **Increasing Design Costs**

- Exponentially increasing design costs

- Nano-scale technologies are not analog friendly

- o Reducing voltage headroom

- o Increasing process variation

- o Increasing layout-dependency

- 1<sup>st</sup>-time success is critical, hence verification is critical

#DesignCon

IBS, "As Chip Design Costs Skyrocket, 3 nm Process Node Is in Jeopardy," 2020. https://www.extremetech.com/computing/272096-3nm-process-node (accessed on 11 March 2022).

6

(i) informa markets

### Motivation: Tiny Mistakes → Huge Problems

#DesignCor

- "The devil is in the details" Failures often occur at digital/analog boundaries

- "If it's not tested, it doesn't work" Mixed-signal simulations test domain crossing interfaces

- Failures are costly

- o Low-end: metal mask change to fix interface issues (optimistic)

- o High-end: missed market window, squandered investment, unhappy customers, and tarnished reputation

## **Motivation: Solution is to Test Everything**

#### Unit testing

o Block functionality verified against specifications

#### In-situ testing

o Blocks tested in groups within the same domain

#### Interface testing

o Exercises inter-domain connectivity/functionality

#### Validation time is limited

- o Analog circuit simulations are CPU intensive

- o Behavioral models accelerate M/S validation

| SPICE/fast-SPICE not fast enough           |                     |

|--------------------------------------------|---------------------|

| Transistor-gate co-simulation slow         |                     |

| Creating and validating behavioral models  |                     |

| Lack of verification modelsfor AMS IP      |                     |

| Language support for behavioral simulation |                     |

| Modeling and verifiying power intent       |                     |

| Creating test vectors for target coverage  | ants                |

| Verifying connectivity                     | ponses by           |

| VHW/SW co-verification                     | mme. 501 tes        |

| Other                                      | Relative Importance |

///////

#DesignCor

informa markets

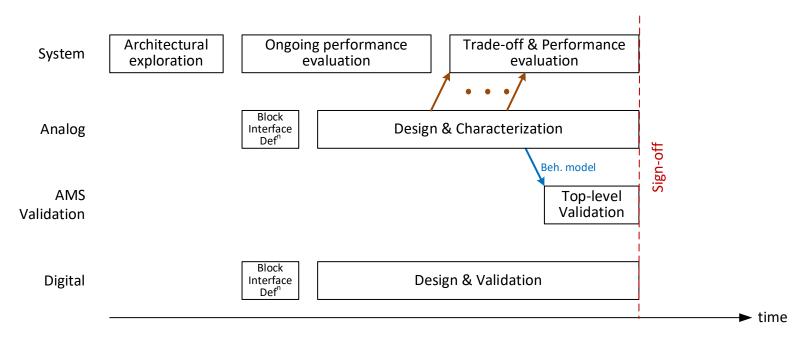

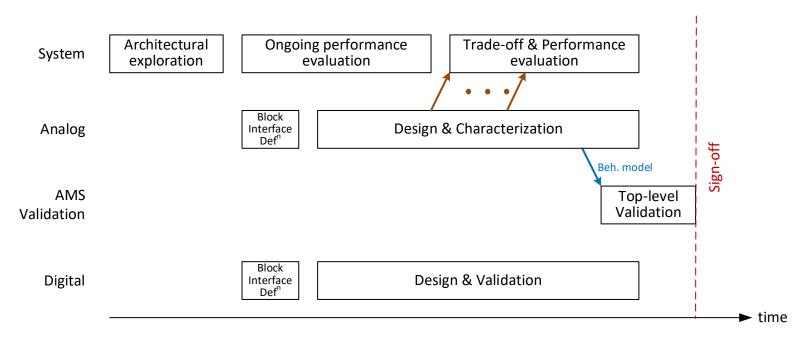

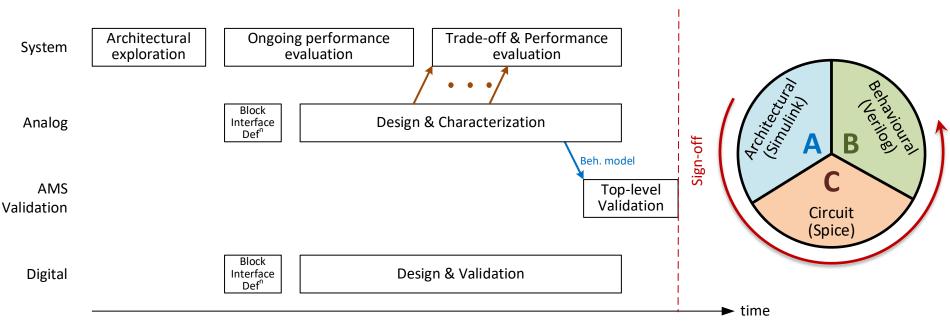

### **Motivation: Typical SerDes Project Lifetime**

- Behavioral models are created late in the project lifecycle or are insufficiently representative

- Behavioral models require manual design in a low-level language: SystemVerilog, C/C++, etc.

#DesignCon

informa markets

### **Motivation: Typical SerDes Project Lifetime**

- Behavioral models are created late in the project lifecycle or are insufficiently representative

- Behavioral models require manual design in a low-level language: SystemVerilog, C/C++, etc.

#DesignCon

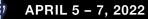

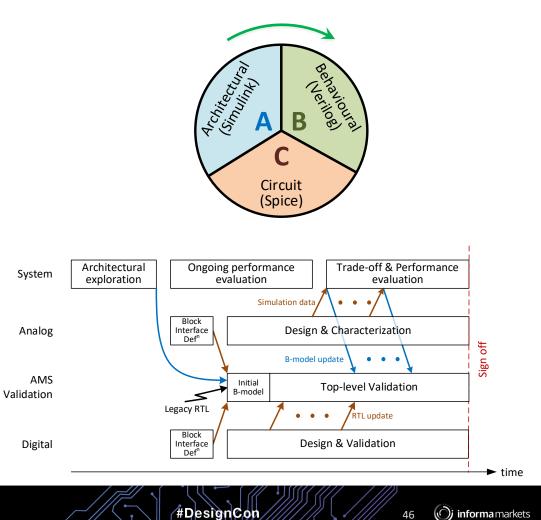

- Model use throughout a SerDes development life-cycle and the ABCs of SerDes models

- Generating B-models from A-models

- C-model design and characterization

- Updating A-model based on C-model characterization

- Automatic B-model refresh from A-model

#DesignCo

informa markets

#### Model use throughout a SerDes development life-cycle and the ABCs of SerDes models

- Generating B-models from A-models

- C-model design and characterization

- Updating A-model based on C-model characterization

- Automatic B-model refresh from A-model

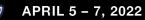

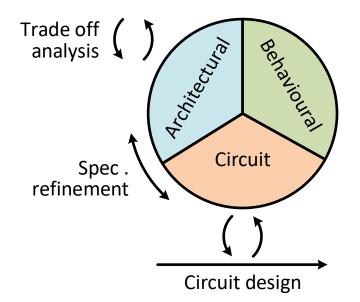

#### **ABC Models**

- Architectural models validate system functionality with different channels

- Behavioral models are used to stand-in for C-models to accelerate validation

- Circuit models make use of circuit simulators and embody the low-level details of the SerDes design

- ABC models are (re)used throughout a SerDes development

#DesignCo

13 (informa markets

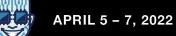

#### **Models Usage Scenarios**

- Requirements and standards drive architectural definition

- Architectural choices are explored using A models

- A models embody design requirements and target functionality/behavior

- Specifications are provided to circuit designers for implementation

#DesignCon

### **Models Usage Scenarios (2)**

- Meeting specs may not be feasible

- o Voltage headroom limitations

- o Technology limitations

- o Power/area limitations

- Design limitations are encountered during circuit design, but design tradeoffs are explored using A models

- For tradeoff analysis, A model is updated to match circuit performance

#DesignCor

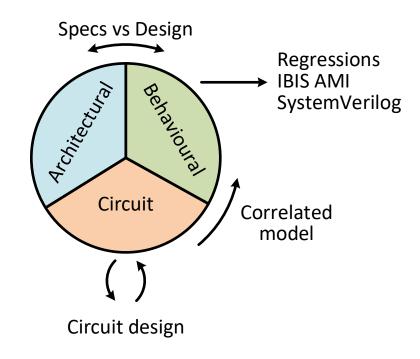

### **Models Usage Scenarios (3)**

#### Behavioral models are manually created

- o Susceptible to human errors

- o Questionable model quality (what's important vs what is not)

- o Requires manual maintenance

- Correlation to circuit models is required

- Enables top-level design vs spec. validation

- IBIS-AMI models = behavioral models

#DesignCor

### Validation Shift-Left: Early B-Models

#DesignCon

- Generated near project start based on specifications embodied in architectural models

- B-models updated and refined as project evolves based on C-model characterization

informa markets

### Validation Shift-Left: Early B-Models

#DesignCon

- Generated near project start based on specifications embodied in architectural models

- B-models updated and refined as project evolves based on C-model characterization

APRIL 5 – 7, 2022

18 (informa markets

- Model use throughout a SerDes development life-cycle and the ABCs of SerDes models

- Generating B-models from A-models

- C-model design and characterization

- Updating A-model based on C-model characterization

- Automatic B-model refresh from A-model

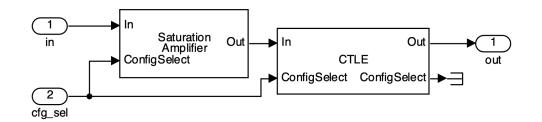

### **A-Model Hierarchy: Receiver Example**

#DesignCon

Matches C-model hierarchy to allow for future block refinement and export

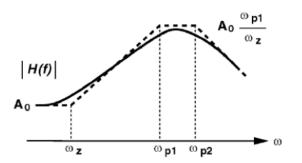

#### **COM-Based CTLE Definition**

- An LTI filter from the system POV

- A continuous-time filter is fully parametrized by pole and zero location, and its gain

• Approach used by COM

o Tuning affected by changing pole or zero locations

#### Represented in discrete-time via

- bilinear transform → IIR implementation

- Sampled impulse response → FIR implementation

#DesignCor

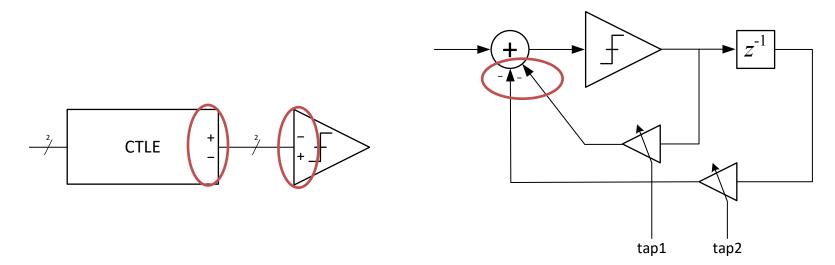

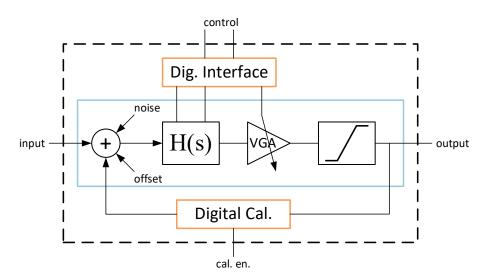

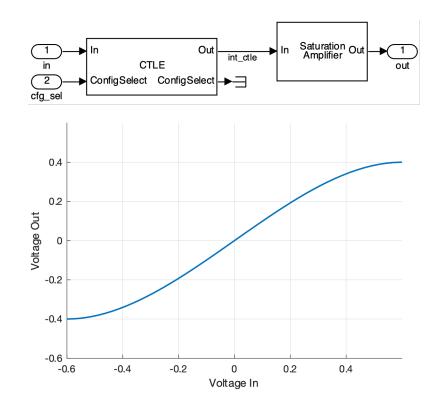

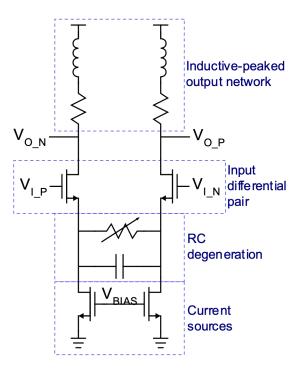

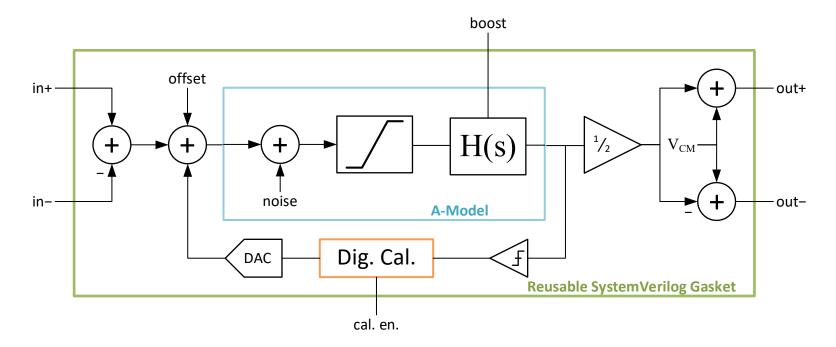

### **CTLE Circuit Block Diagram**

#### Circuit implementation is complex

- o Continuous-time filtering via analog circuits

- o Tuning via digitally controllable resistor/capacitor banks

#### Imperfect and variable circuit characteristics

- Additive circuit noise

- Dynamic range compression due to voltage headroom limits

- o Transistor mismatches lead to unwanted offsets

- o Offsets can be removed via digital trimming

#### Required behavior is captured by A-model

◦ Some effects do not need to be modeled: e.g., offset and offset-compensation → yet, residual offset is important

#DesignCon

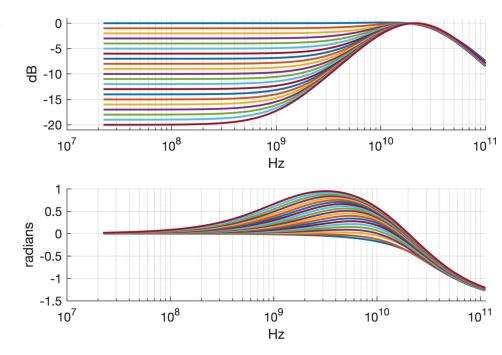

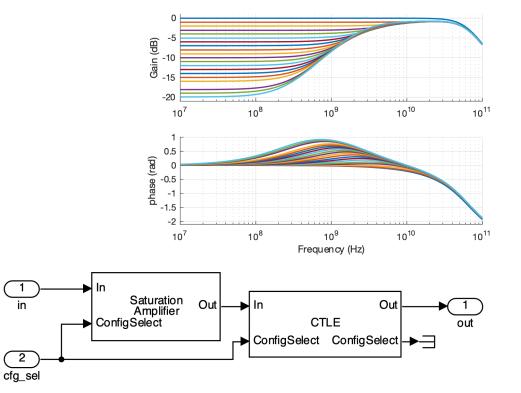

### **A-Model Target CTLE Frequency Response**

- Family of digitally selectable filter responses

- o Boost at 20GHz

- DC attenuation: -20 to 0dB in 1dB steps

- Input referred noise needs to be estimated

- o It is shaped by the CTLE frequency response

- LTI behavior is captured. What about nonlinear effects?

#DesignCor

(informa markets

### **CTLE Output Nonlinearity Model**

#### CTLE can be input, or output voltage limited

- Depending circuit topology chosen, biasing levels, etc.

- o Limiting impacts voltage input/output swing

- CTLE designed as a differential circuit

- o Soft limiting as differential pair becomes less linear

- o Approximated by arctangent function

- Expected to be output limited

#DesignCon

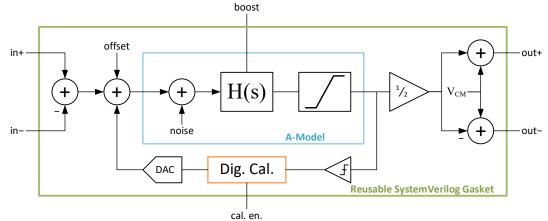

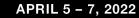

### **Complete CTLE B-Model**

#### 3 constituent pieces

- o Core functionality based on A-model

- o Interface gasket re-usable RTL

- o Digital calibration engine synthesizable RTL

- Single-ended to differential conversion performed by re-usable SystemVerilog

- DAC and slicer abstracted in example B-model – can be exported A-models

- If circuit implementation changes, then A-model functionality will change

#DesignCor

APRIL 5 – 7, 2022

### SystemVerilog Gasket

#### Instantiates

- o Digital calibration engine synthesizable RTL

- o Core filter behavior exported A-model

- SE-to-diff. conversion 3-lines of code

- DAC and comparator modelled directly

- The rest is port and net definitions

- Offset & common-mode are parameters

```

module ctle #(

parameter offset = 0.0.

parameter cm = 0.5

) (

input arst b, // Asynchronous reset

input cm clk, // common-mode compensation clock

input cm cal en, // common-mode calibration enable

input real inp, // CTLE differential input +

input real inm, // CTLE differential input -

input byte unsigned boost, // boost setting

output real outp, // CTLE differential output +

output real outm // CTLE differential output -

);

real in, offset comp, out;

req out q;

wire signed [7:0] offset comp dig;

always @(*) begin: CTLE step

offset comp = offset comp dig * 0.125/128; // offset DAC model

in = inp - inm + offset - offset comp:

outp = cm + out/2:

outm = cm - out/2:

end

// Clocked comparator

always @(posedge cm clk)

out q <= cm cal en? outp > outm: 1'b0;

// CTLE digital offset calibration

ctle cm cal #(.M(8), .N (12)) ctle cm cal (.arst b(arst b), .clk(cm clk),

.en(cm cal en), .sense(out q), .comp(offset comp dig));

// CTLE B-model core (based on exported A-model)

CTLE dpi ctle core(.ctle in(in), .cfg sel(boost), .out(out));

endmodule

```

#DesignCor

26 (informa markets

- Model use throughout a SerDes development life-cycle and the ABCs of SerDes models

- Generating B-models from A-models

- o Correlation of A- and B-model

- C-model design and characterization

- Updating A-model based on C-model characterization

- Automatic B-model refresh from A-model

2022

#DesignCon

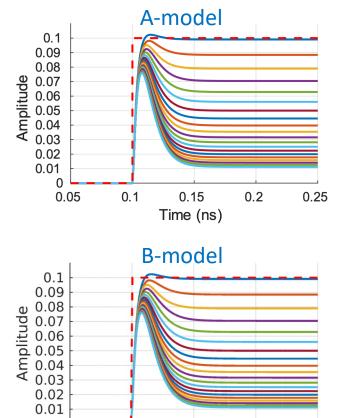

# A- vs B-model: Step Response

- Step response fully characterizes CTLE

- 100mV step does not result in output-limiting

- Responses for all CTLE boost settings shown

- No distinguishable difference between A and B models

0.05

#DesignCon

0.1

//// 28

0.15

Time (ns)

0.2

0.25

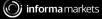

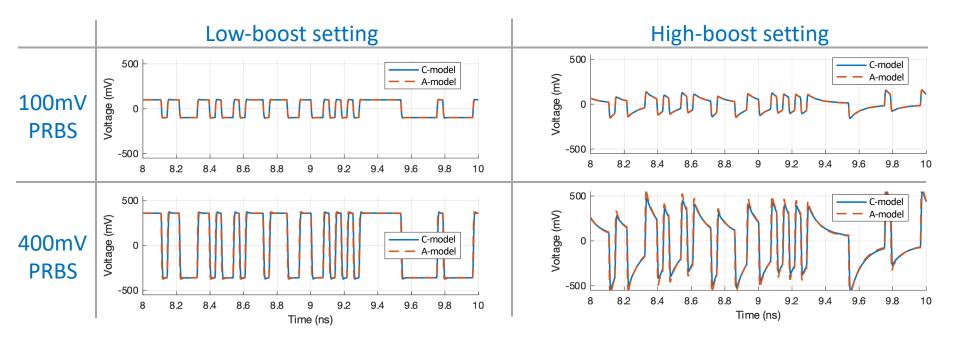

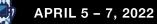

### A- vs B-model: Large/Small Amplitude PRBS

#DesignCon

Simulink and Verilog outputs overlaid. Matched across amplitude and boost settings.

APRIL 5 – 7, 2022

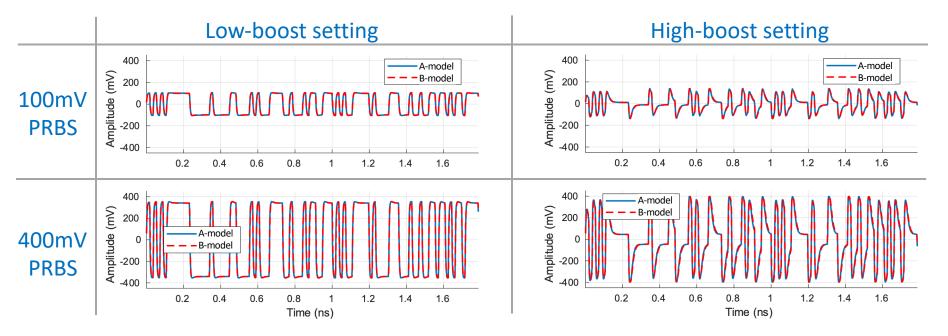

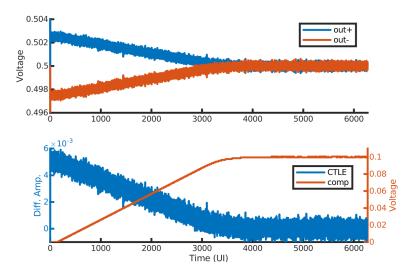

#### **CTLE Offset Calibration Engine**

- Input-referred offset is a DC phenomenon

- Measured at CTLE output with shorted inputs

- CTLE output is asynchronously sampled

- ±1 sample decisions are digitally integrated

- Top N integrator bits drive compensation DAC

- Compensated when ±1 are equally probable

```

module ctle cm cal #(

parameter M = 8,

parameter N = 16

) (

input arst b, // Asynchronous reset

input clk,

// clock

input cal en, // engine enable

input sense, // comparator sense output

output signed [M-1:0] comp); // compensation code

reg signed [N-1:0] control;

assign comp = control[N - 1 -: M];

always @(posedge clk, negedge arst b)

if (~arst b)

control = {N{1'd0}};

else

control = control + (cal en? (sense? 1'sd1: -1'sd1): 1'd0);

endmodule

```

///////

#DesignCo

#### **CTLE Offset Calibration**

#### Verilog-based testbench

- o Supplies a random offset to CTLE gasket

- o Drives CTLE inputs to common mode

- o CTLE input-referred noise is added

#### Ironically:

- o Got the feedback polarity wrong!

- o Didn't account for boost dependent DC attenuation

- o Both debugged with early CTLE B-model

#DesignCor

- Model use throughout a SerDes development life-cycle and the ABCs of SerDes models

- Generating B-models from A-models

- C-model design and characterization

- Updating A-model based on C-model characterization

- Automatic B-model refresh from A-model

#### **CTLE C-Model**

Flow demonstrated via simplified CTLE circuit

#### C-model characterized via simulations

- o AC simulations to get frequency dependent response

- o DC simulations to get large-signal compression

- o MC simulations to measure expected input-offset

- o Noise simulations to determine input-referred noise

- o etc.

- Analog simulation results are used to refine A-model

#DesignCor

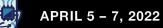

### **Desired vs Simulated Freq. Response**

#DesignCon

Visible disparity used to highlight change due to A-model refresh

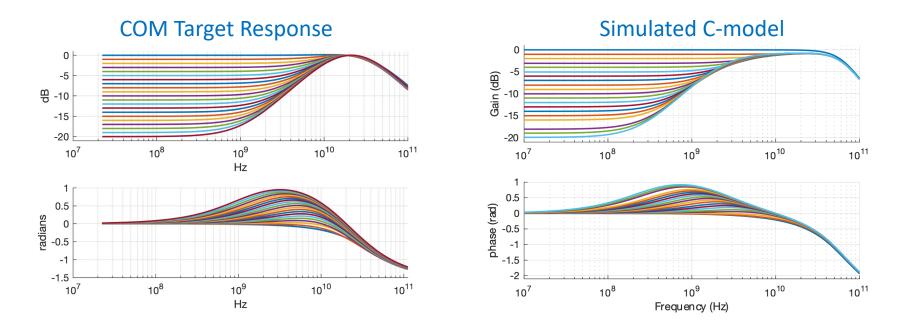

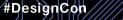

#### **Simulated Large Signal Compression**

- Differential DC sweep about common mode

- Simulated V<sub>OUT</sub> vs V<sub>IN</sub> curve normalized by DC gain to get input or output limiting

- Plot shows CTLE is input limited, rather than output limited

#DesignCor

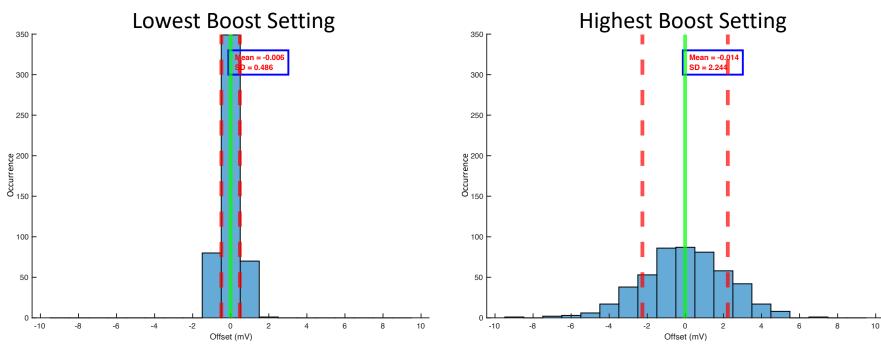

### **Simulated CTLE Input-Referred Offset**

- The simulated CTLE offset is within the offset compensation range (±100mV)

- Information can used to decrease the feedback DAC dynamic range: no impact on digital

#DesignCon

APRIL 5 – 7, 2022

- Model use throughout a SerDes development life-cycle and the ABCs of SerDes models

- Generating B-models from A-models

- C-model design and characterization

- Updating A-model based on C-model characterization

- Automatic B-model refresh from A-model

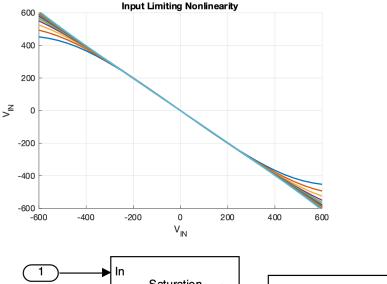

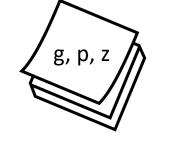

### **A-Model Update**

- Simulated input limiting used to configure saturating amplifier

- Rational fit used to match simulated frequency response

- o Compact gain, pole & zero representation

- GPZ matrix used to configure CTLE model

#DesignCon

### **A-Model Update**

- Simulated input limiting used to configure saturating amplifier

- Rational fit used to match simulated frequency response

- o Compact gain, pole & zero representation

- GPZ matrix used to configure CTLE model

#DesignCon

### **A-Model Update**

- Simulated input limiting used to configure saturating amplifier

- Rational fit used to match simulated frequency response

- o Compact gain, pole & zero representation

- GPZ matrix used to configure CTLE model

#DesignCon

### **C-to-A model Correlation**

#DesignCon

- PRBS sequence used to correlate C-model to A-model behavior

- Well matched, but could do better by modeling output limiting behavior as well

41 (

- Model use throughout a SerDes development life-cycle and the ABCs of SerDes models

- Generating B-models from A-models

- C-model design and characterization

- Updating A-model based on C-model characterization

- Automatic B-model refresh from A-model

#### How do we refresh the B-Model

#DesignCon

Simple! Just re-export the DPI, based on the updated Simulink model

43 🔘

#### How do we refresh the B-Model

#DesignCon

Simple! Just re-export the DPI, based on the updated Simulink model

44 🔘

### **B-to-A Model Correlation**

#DesignCon

- Very well-matched behavior

- Improvements in C-to-A correlation would be manifested in B-model as well

APRIL 5 – 7, 2022

#### Conclusion

Initial A-models embody circuit specs.

#### Demonstrated flow for a CTLE

- Early B-model based on architectural models

- o C-model was designed and characterized

- Updated A-model based on simulation data

- Regenerated updated B-model

#### **Enables validation shift-left**

- Earlier start 0

- Better test coverage Ο

- Higher sign-off confidence Ο

#### Follow up with us after the conference

Engage with us <u>info@serialinksystems.com</u>

Visit us at <u>www.serialinksystems.com</u>

#DesignCon