# Welcome to DESIGNCON® 2022 WHERE THE CHIP MEETS THE BOARD

#### Conference

April 5 – 7, 2022

**Expo** April 6 – 7, 2022

Santa Clara Convention Center

#DesignCon

# Parametric System Model of a 112Gbps ADC-based SerDes for Architectural, Design & Validation Project Phases

Aleksey Tyshchenko, SeriaLink Systems

David Halupka (SeriaLink Systems) Venu Balasubramonian, Lenin Patra (Marvell Semiconductor)

APRIL 5 – 7, 2022

#DesignCon

#### **SPEAKER**

#### Aleksey Tyshchenko

Founder, SeriaLink Systems aleksey@serialinksystems.com | www.serialinksystems.com

SeriaLink Systems is working on building a configurable modeling flow to support SerDes projects through their entire life cycle: from architecture definition, through analog and digital design, to design validation. Aleksey has been working on behavioral modeling of high-speed SerDes systems, architecture analysis, adaptation, and signal integrity with multi-standard SerDes IP teams at V Semi and Intel.

APRIL 5 – 7, 2022

#DesignCon

(i) informa markets

#### Outline

- Motivation

- System Modeling through SerDes Development

- Parametric DAC-based TX Model

- Parametric ADC-based RX Model

- Model Correlation

- Conclusion

#DesignCon

### **Motivation**

- Multiple system models support SerDes IP development

- These internal development models are rarely shared with system integrators

- At leading-edge data rates, SerDes IP and channels are developed concurrently

- However, limited modeling options available for technical interaction

- COM drives specification alignment at the project onset

- IBIS-AMI drives signal integrity sign-off at the project end

- During majority of design activities, models suitable for sharing are unavailable

- Is it possible to unify SerDes system modeling activities into a single framework?

- Can the unified models facilitate technical interaction between IP vendors and system integrators?

#DesignCor

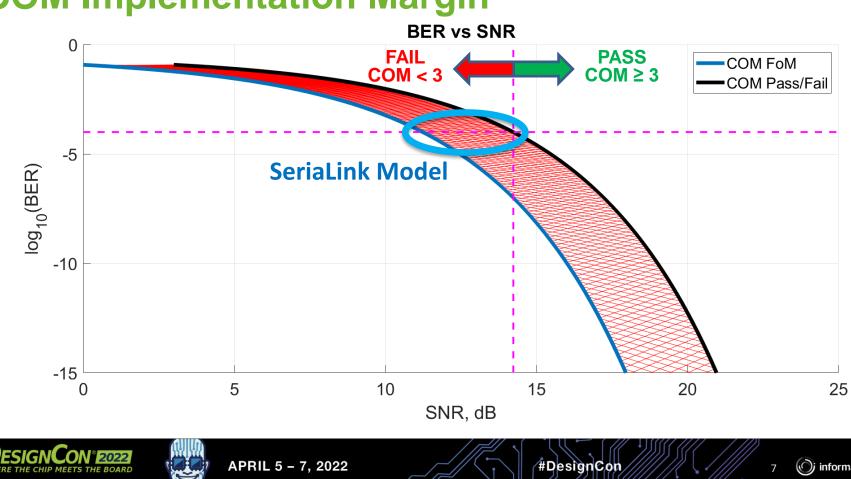

#### **BER vs SNR** 0 FAIL PASS COM FoM $COM \ge 3$ **COM** < 3 COM Pass/Fail -5 log<sub>10</sub>(BER) -10 -15 5 10 15 20 25 0 SNR, dB APRIL 5 – 7, 2022 (); informa markets #DesignCon 6

**COM Implementation Margin**

#### **COM Implementation Margin**

(); informa markets

### Outline

#### Motivation

- System Modeling through SerDes Development

- Parametric DAC-based TX Model

- Parametric ADC-based RX Model

- Model Correlation

- Conclusion

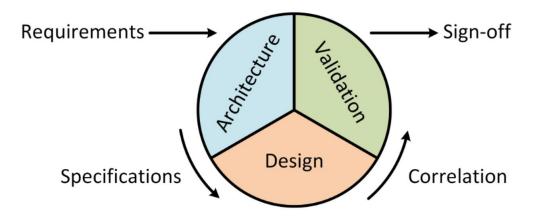

# System Models in SerDes IP Development

- Multiple system models support SerDes IP development activities

- Approximate (abstract) models guide architectural exploration and design specifications

- Detailed models support design activities by evaluating performance trade-offs between different blocks

- Port-accurate correlated models drive mixed-signal validation before project sign-off

- These individual models are rarely shared with system integrators due to logistics and IP protection concerns

- Proposed unified modeling framework can replace multiple models with one model, suitable for sharing

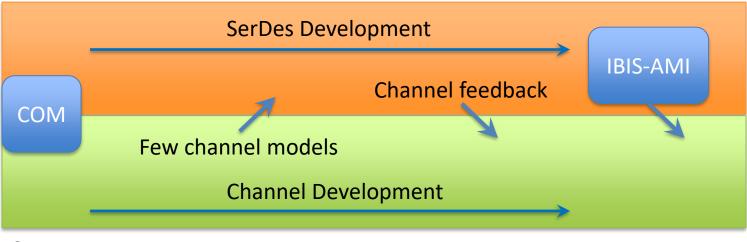

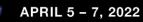

# **Interaction: IP Supplies and System Integrators**

#### **SerDes IP Provider**

#### System Integrator

• COM facilitates alignment at the project onset, for standard-compliant and custom SerDes systems

#DesignCon

- IBIS-AMI enables signal integrity validation and sign-off at the end of the development cycle

- No suitable models are available for sharing during the majority of design activities

# **Interaction: IP Supplies and System Integrators**

#### **SerDes IP Provider**

#### System Integrator

- Augment COM and IBIS-AMI with a parametric SerDes model that reflects IP performance

- Obfuscated code at block level for IP protection, exposed top level signals for observability

- Quantitative feedback between teams early in development process, in a regressable self-contained test-bench

//////

#DesignCon

### Outline

#### Motivation

- System Modeling through SerDes Development

- Parametric DAC-based TX Model

- Parametric ADC-based RX Model

- Model Correlation

- Conclusion

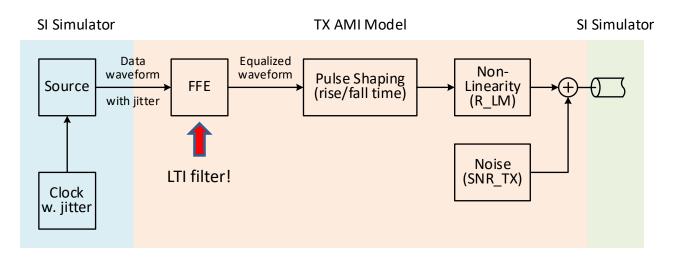

# **COM-parametric TX Model in IBIS-AMI Framework**

#DesignCon

- Includes same components as COM reference TX, supports statistical and time domain simulations

- COM-parametric TX model with two intended use cases

- Can be configured to represent a standard-compliant TX

- Can be configured to represent measured TX performance

13

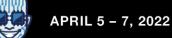

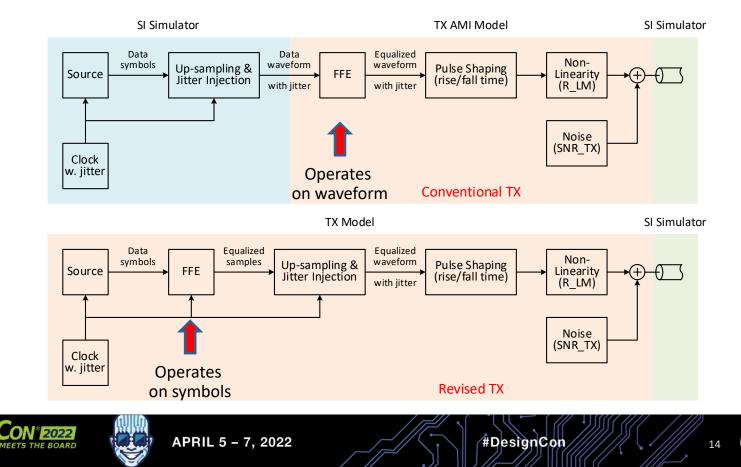

## **Revised TX Model**

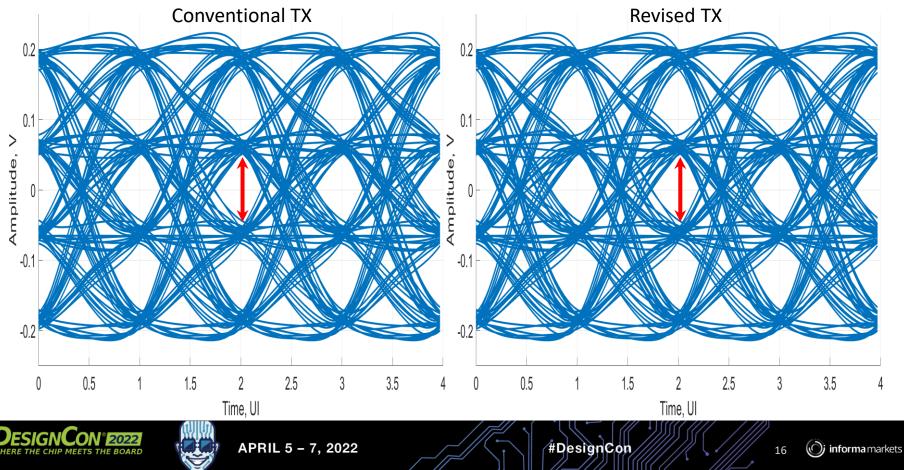

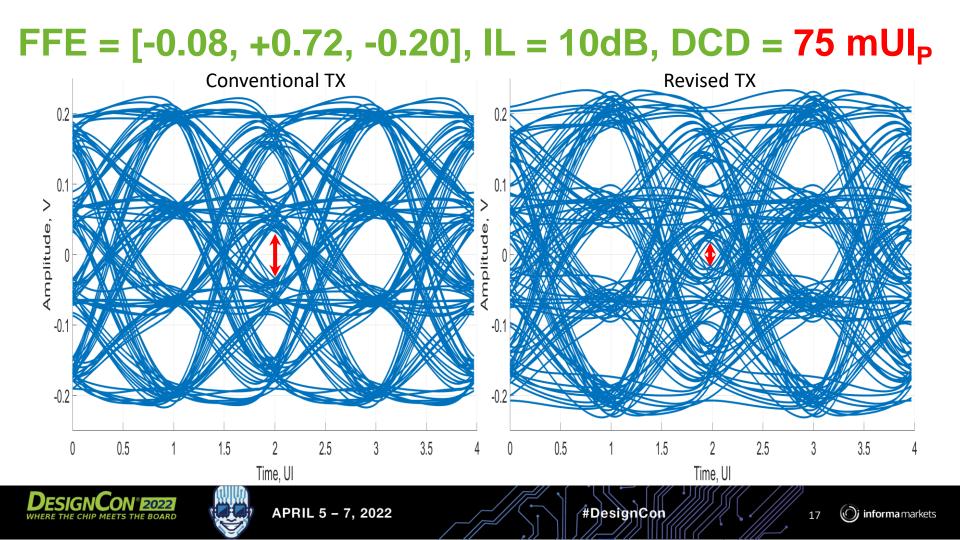

### **Channel Response: IL = 10 dB**

# $FFE = [-0.08, +0.72, -0.20], IL = 10dB, DCD = 0 mUI_P$

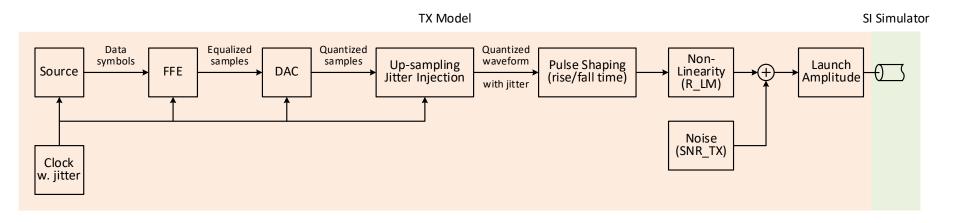

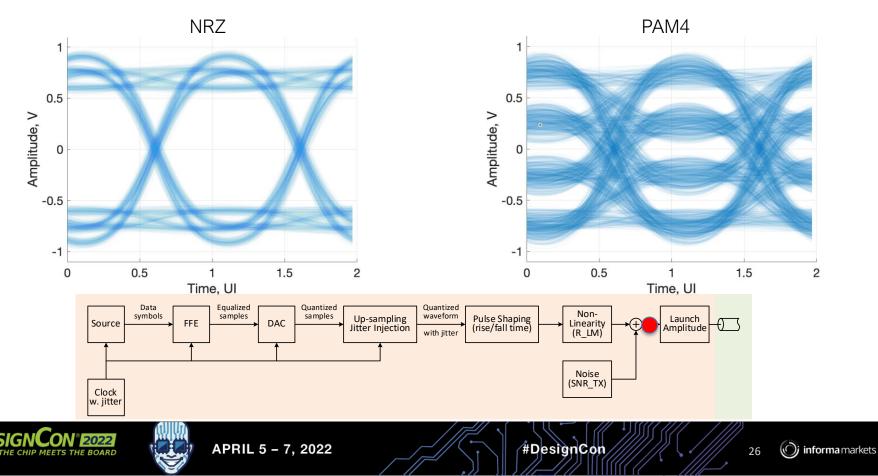

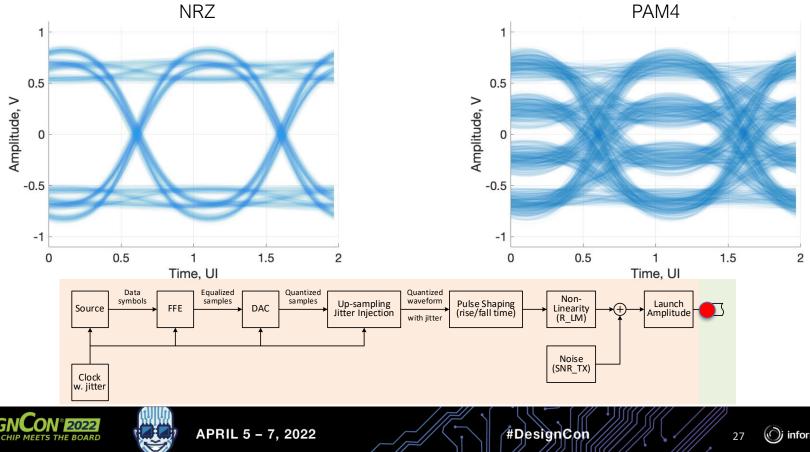

# **Proposed DAC-based TX Model**

- Access to equalized samples enables modeling DAC-based TX architectures

- Direct access to data bits and symbols opens up an option to add FEC into the link model

- Enables exploration of higher order PAM modulations

- Blocks are instances of corresponding classes, configured at simulation start

- Block implementation can be obfuscated for IP protection when models are shared with system integrators

#DesignCon

(informa markets

18

All signals between blocks remain observable

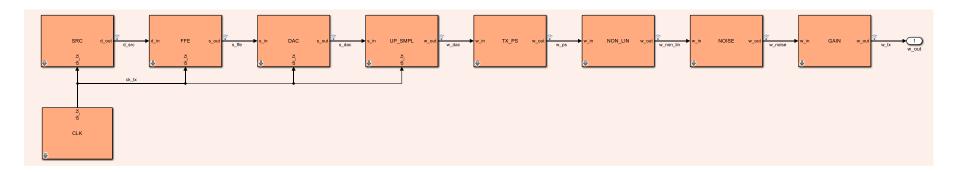

# **Proposed DAC-based TX Model in Simulink**

- Access to equalized samples enables modeling DAC-based TX architectures

- Direct access to data bits and symbols opens up an option to add FEC into the link model

- Enables exploration of higher order PAM modulations

- Blocks are instances of corresponding classes, configured at simulation start

- Block implementation can be obfuscated for IP protection when models are shared with system integrators

#DesignCon

All signals between blocks remain observable

informa markets

19

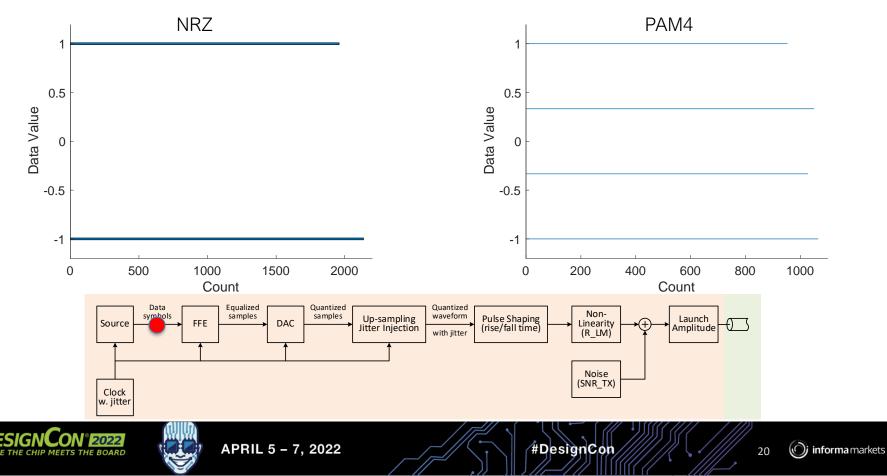

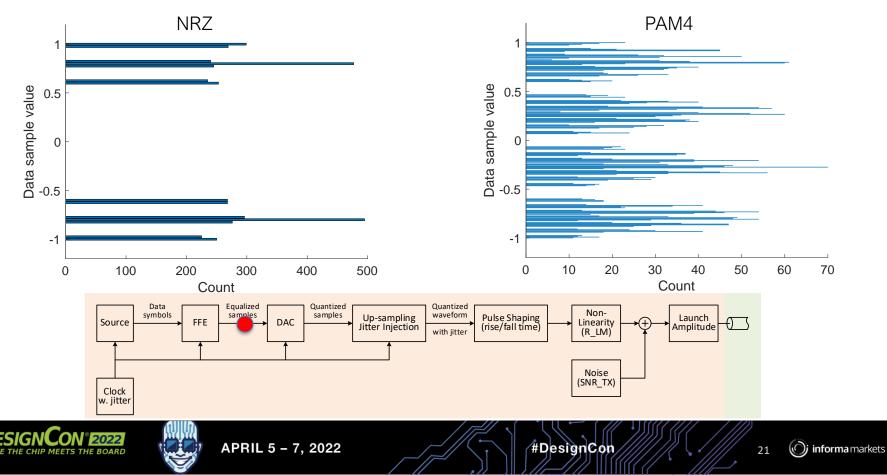

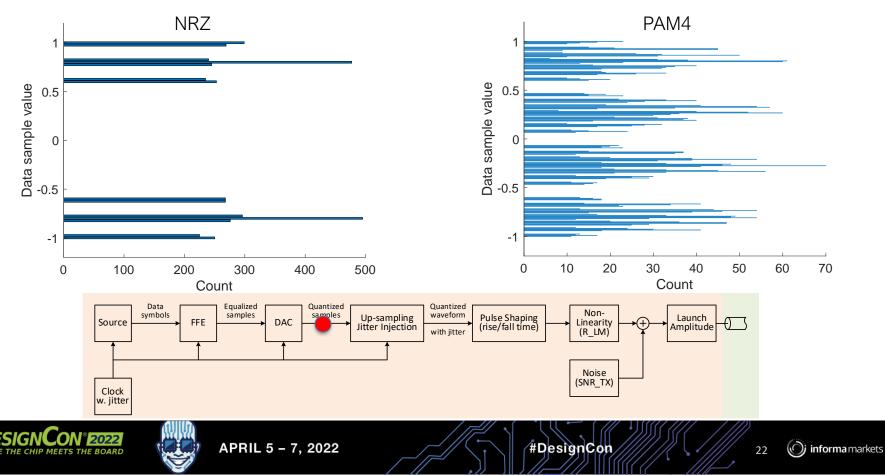

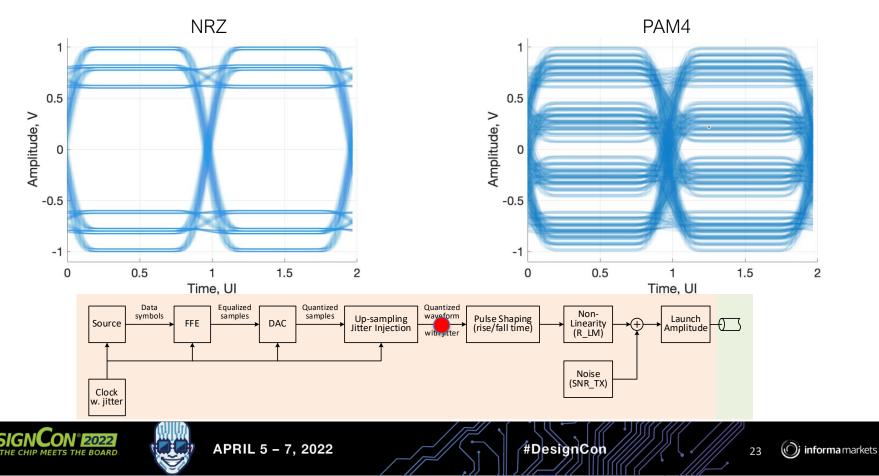

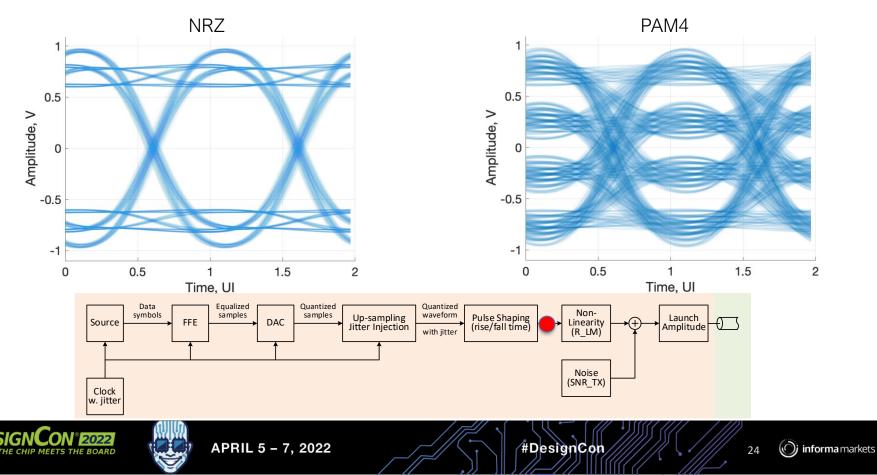

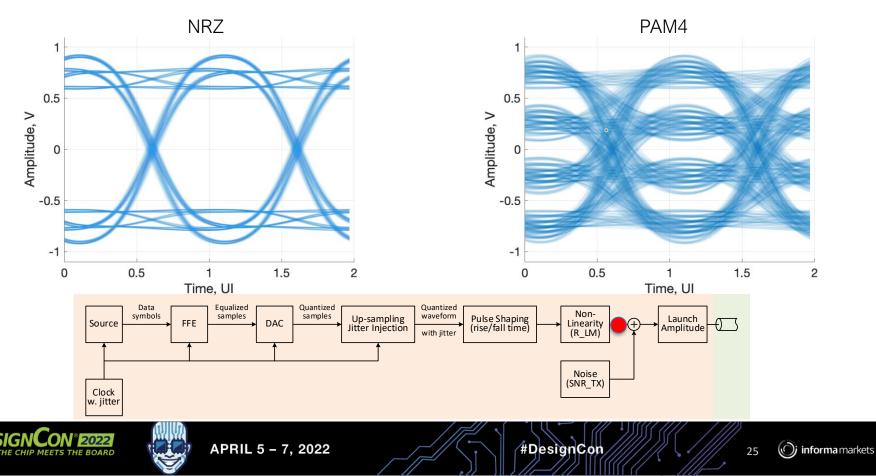

#### **TX Model Observability: Data Source**

### **TX Model Observability: FFE**

### **TX Model Observability: DAC**

### **TX Model Observability: Jitter Injection**

### **TX Model Observability: Rise/Fall Time Adjust**

### **TX Model Observability: Non-Linearity**

### **TX Model Observability: Noise**

### **TX Model Observability: Launch Amplitude**

informa markets

# **TX Model Configurability**

|                                                                | COM          | SeriaLink Model |

|----------------------------------------------------------------|--------------|-----------------|

| Data pattern: PRBS sequence, repeating pattern, data from file | X            | $\checkmark$    |

| Modulation                                                     | $\checkmark$ | $\checkmark$    |

| Number of FFE taps, tap ranges                                 | $\checkmark$ | $\checkmark$    |

| DAC resolution                                                 | ×            | $\checkmark$    |

| Basic jitter sources                                           | ✓            | $\checkmark$    |

| Advanced jitter sources                                        | ×            | $\checkmark$    |

| Rise / fall time, launch amplitude                             | $\checkmark$ | $\checkmark$    |

| Non-linearity, voltage noise                                   | $\checkmark$ | $\checkmark$    |

| Time domain simulations                                        | X            | <b>V</b>        |

#DesignCon

### Outline

- Motivation

- System Modeling through SerDes Development

- Parametric DAC-based TX Model

#### Parametric ADC-based RX Model

- Model Correlation

- Conclusion

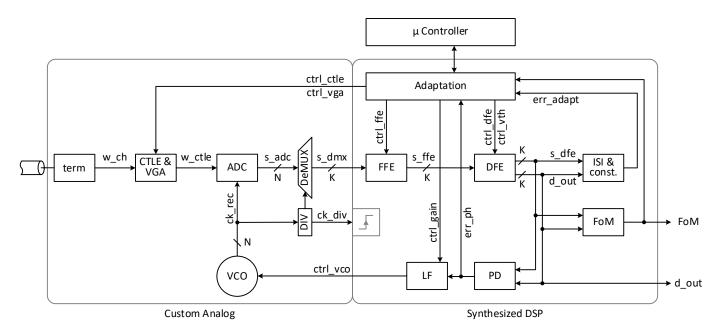

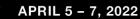

# **Proposed ADC-based RX Model**

#DesignCon

- Design-representative RX model, includes top-level blocks with their interfaces

- Configurable CTLE, time-interleaved ADC sampling, frame-based DSP

- Representative block interfaces allow modeling calibration and adaptation in time domain

30

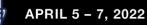

# **Proposed ADC-based RX Model in Simulink**

- Blocks can be added or removed to focus on a certain aspect of SerDes behavior

- Direct access to data bits and symbols opens up an option to add FEC into the link model

- Enables exploration of higher order PAM modulations

- Blocks are instances of corresponding classes, configured at simulation start

- Block implementation can be obfuscated for IP protection when models are shared with system integrators

#DesignCor

All signals between blocks remain observable

31

(i) informa markets

### **RX Model Observability: CTLE**

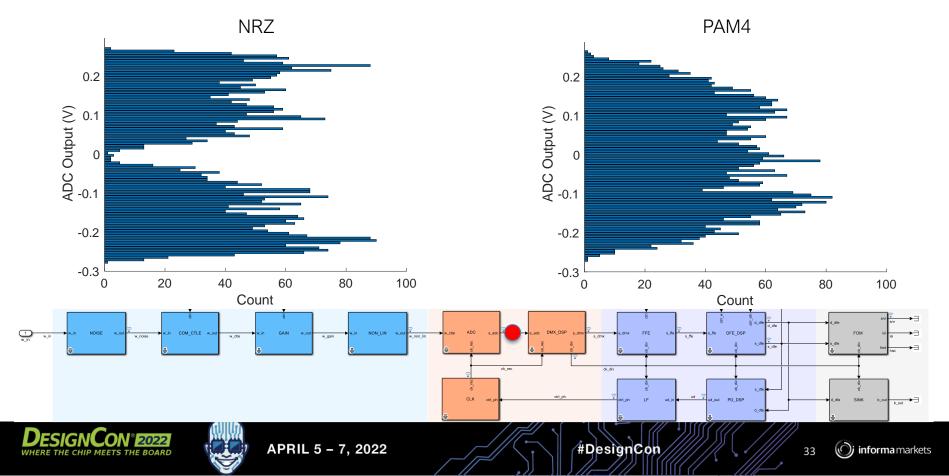

#### **RX Model Observability: ADC**

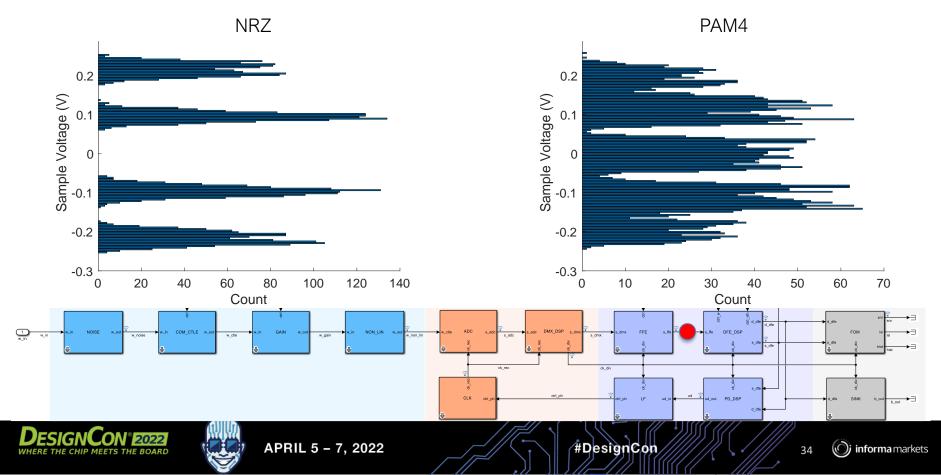

### **RX Model Observability: FFE**

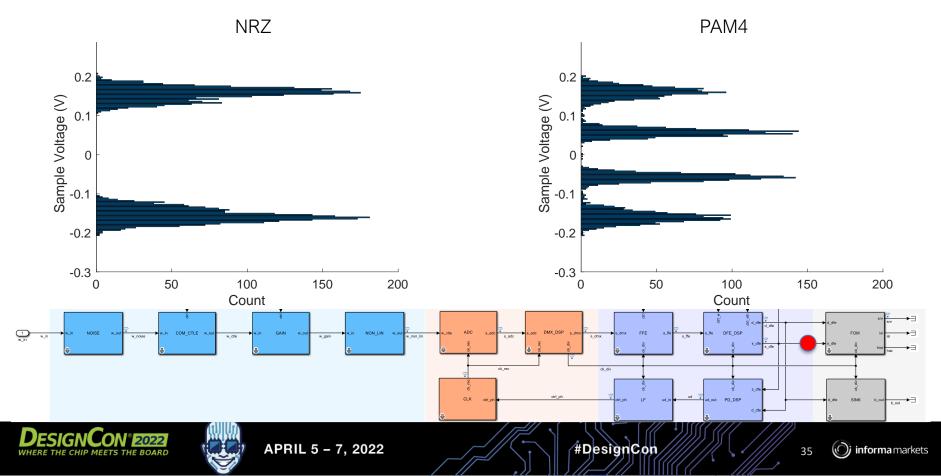

#### **RX Model Observability: DFE**

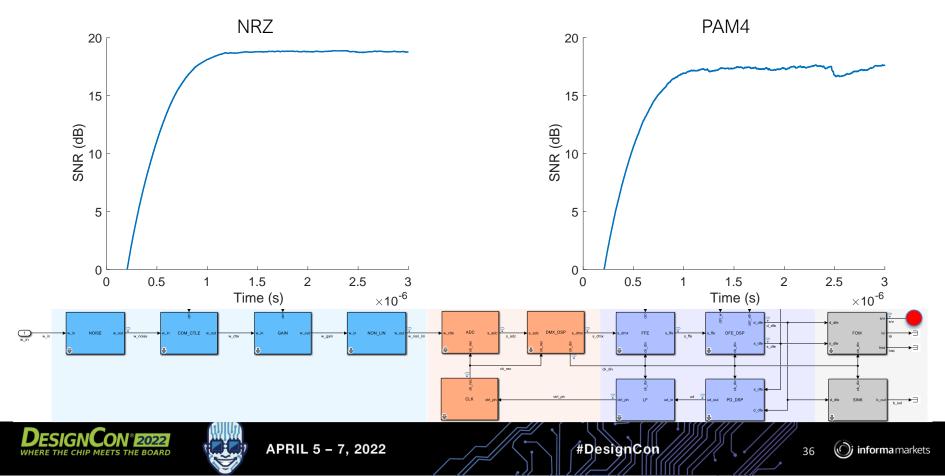

#### **RX Model Observability: SNR**

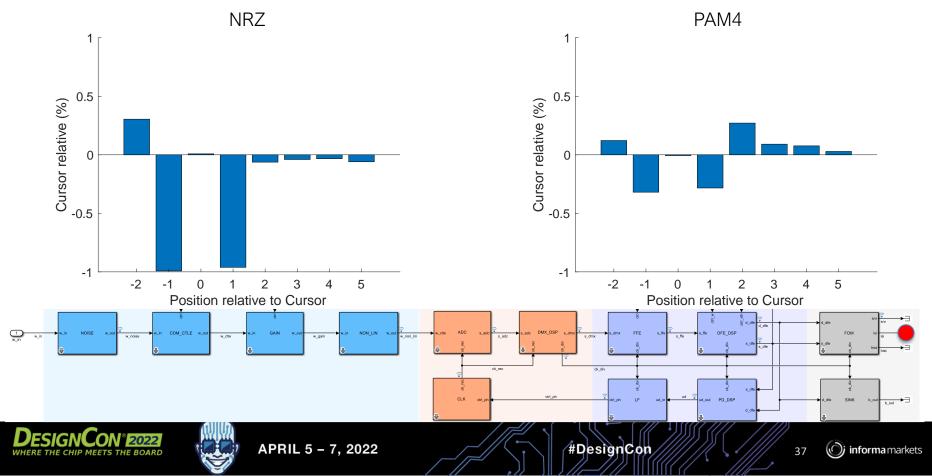

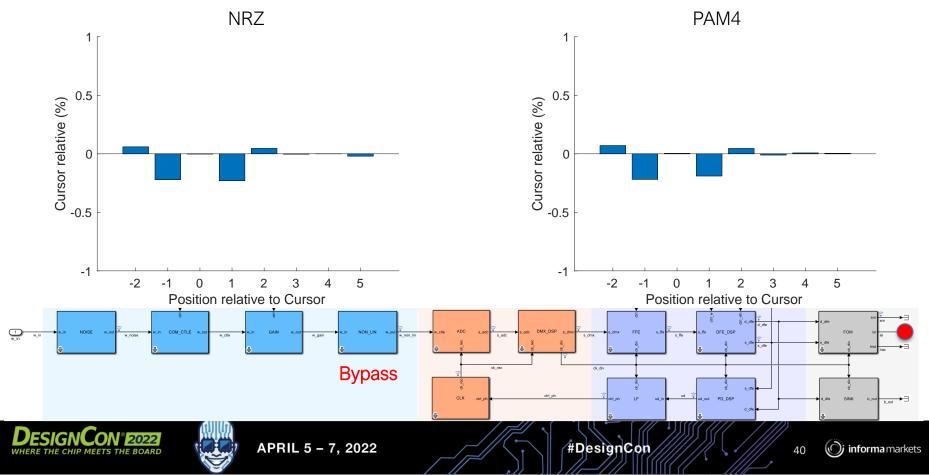

#### **RX Model Observability: Residual ISI**

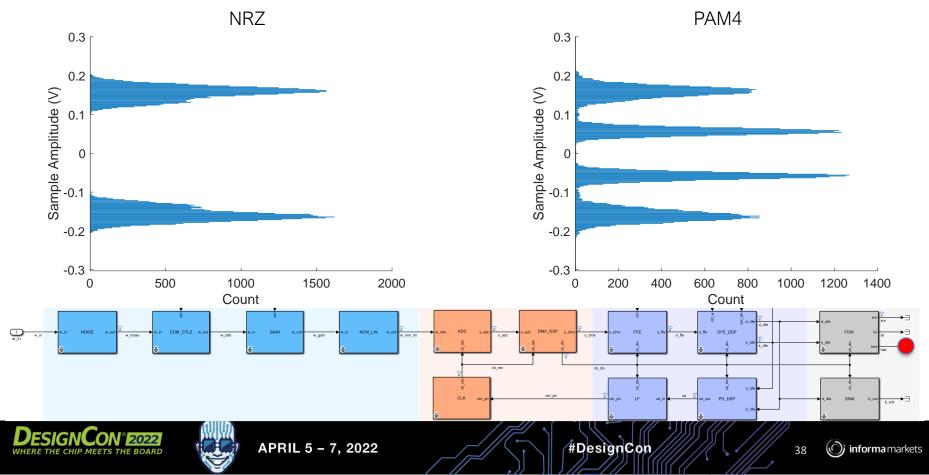

### **RX Model Observability: Amplitude Histogram**

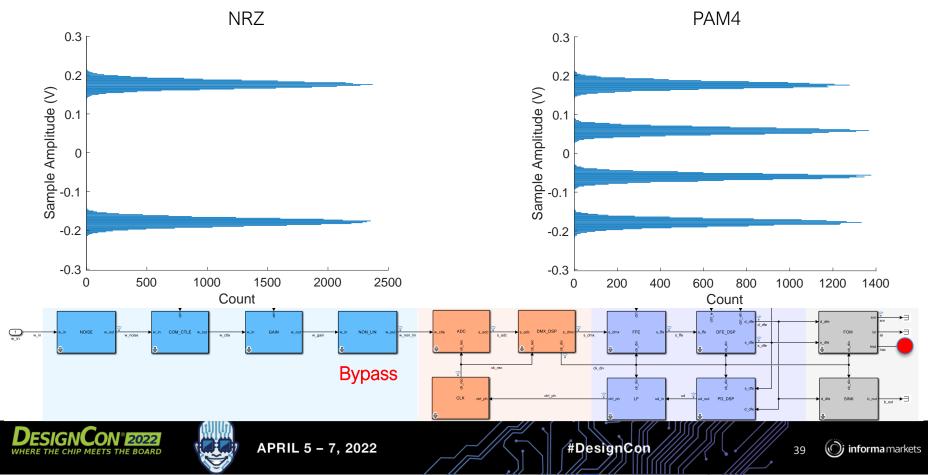

### **RX Model Observability: Non-Linearity OFF**

### **RX Model Observability: Non-Linearity OFF**

# **RX Model Coverage and Configurability, 1 of 2**

|                                             | СОМ          | SeriaLink Model |

|---------------------------------------------|--------------|-----------------|

| Input-referred noise PSD                    | V            | <b>V</b>        |

| CTLE transfer characteristic                | $\checkmark$ | $\checkmark$    |

| VGA gain range and step size                | ×            | $\checkmark$    |

| CTLE & VGA non-linearity                    | ×            | <b>V</b>        |

| Number of clock phases                      | ×            | V V             |

| Clock jitter, residual phase mismatch       | ×            | $\checkmark$    |

| ADC time-interleaving depth, dynamic range  | ×            | $\checkmark$    |

| ADC nominal and effective resolution (ENOB) | ×            | $\checkmark$    |

| Clock recovery loop dynamics                | ×            | V V             |

#DesignCon

41

# **RX Model Coverage and Configurability, 2 of 2**

|                                                         | СОМ          | SeriaLink Model |

|---------------------------------------------------------|--------------|-----------------|

| Number of FFE taps, tap ranges                          | $\checkmark$ | $\checkmark$    |

| Number of DFE taps, tap ranges                          | $\checkmark$ | $\checkmark$    |

| FFE and DFE resolution in DSP                           | ×            | $\checkmark$    |

| DSP operating speed, sample demultiplexing depth        | ×            | $\checkmark$    |

| Latency due to sampling and demultiplexing              | ×            | $\checkmark$    |

| Phase detector pattern dependence                       | ×            | $\checkmark$    |

| Interaction between phase recovery and adaptation loops | ×            | $\checkmark$    |

| Representative time domain adaptation algorithms        | ×            | $\checkmark$    |

| Option to add FEC                                       | ×            | $\checkmark$    |

#DesignCon

### Outline

- Motivation

- System Modeling through SerDes Development

- Parametric DAC-based TX Model

- Parametric ADC-based RX Model

- Model Correlation

- Conclusion

APRIL 5 – 7, 2022

#DesignCon

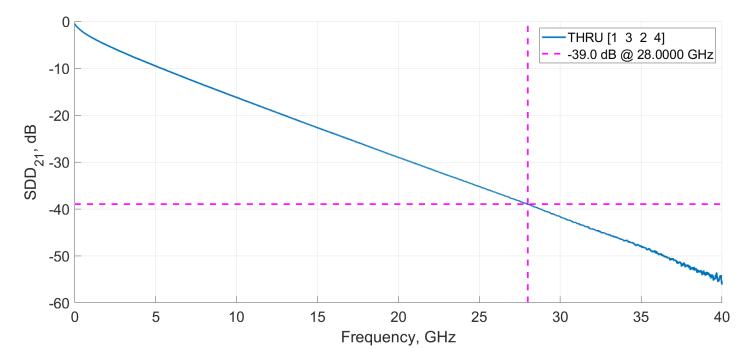

## **Channel Response Used for Model Correlation**

#DesignCon

Same channel was used in measurement and simulations for correlation purposes

44 (Oj

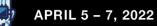

# Model Correlation Methodology at 112 Gb/s

- TX and RX configured consistently with SerDes IP and its corresponding IBIS-AMI model

- BER of 10<sup>-7</sup> is measured in the lab, SNR of 21.5 dB is simulated using IBIS-AMI and SeriaLink models

#DesignCon

SNR-to-BER curve is used to establish correlation between SerDes IP and system models

45 🜘

# Conclusion

- Explored system modeling in SerDes IP development

- Limited technical interaction between SerDes providers & system integrators due to lack of adequate models

- Proposed parametric SerDes system modeling framework SeriaLink Model

- TX and RX modeling details enable looking inside COM implementation margin

- SeriaLink Model parametrization allows quick and simple model configuration to reflect actual SerDes IP

- Model observability is well beyond IBIS-AMI models, enabling channel / SerDes co-optimization

- SeriaLink Model allows code obfuscation at block level for IP protection, and for model sharing between teams

#DesignCon

• Proposed model was correlated with 112 Gb/s SerDes using SNR and BER as correlation metrics

46

(informa markets

# **MORE INFORMATION**

- www.serialinksystems.com

- info@serialinksystems.com

47